桁上げ先見方式について、まずは述べる。

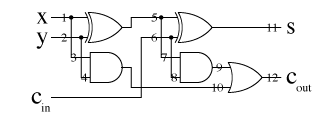

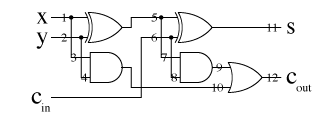

XiとYiを、XORゲートで結んだ出力をPi、ANDゲートで結んだものをGiとする。以下、この入力で考える。1ビットの場合、C0とP0をANDでむすび、それをORで結べばよい。ゲート2個で、ワイヤ−5本である。

nビットの場合、ゲート数は、2+4+6+・・・・・・=n*n+n、ワイヤーは、5+9+13+17+・・・・・・・=2n*n+3n。GやPを作るのに、ゲートを2n+2、ワイヤーを4n+4使用し、AND,XOR,ORの電源に6本のワイヤーを使う。合計するとゲートをn*n+3n+2個、ワイヤーを2n*n+7n+10本使用する。(ただし、n*nとは、nの2乗のこと)

桁上げ先見方式のみを使用すると、桁数が増えた場合は、二次関数的にゲート数が増える。ほかの高速化方法や、高速化しない方法と組み合わせて使うことが多いようだ。単独では、高速化の意義が薄れるので、16ビットくらいまでのときしか使わないようだ。

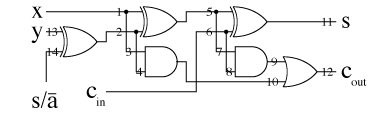

あまりよく分からないのでn/2ビットずつ計算した場合を考えたい。(nは偶数) n/2ビット全加算機では5n/2個の論理ゲートと(11n+1)/2本のワイヤがいる。 n/2ビット全加算機は全部で3つ必要。

次にマルチプレクサを考える。しかしよくわからない。だから違っているかもしれません。 必要な論理ゲートはANDがn個、ORがn/2個、さらにビット反転のためのNANDがn/2個。 ワイヤは出力にさらにn-1本、ビット反転で(n/2)*3本使う。

そしてANDからn本、ORからn/2本のびるので論理ゲートは全体で

(5n/2)*3+n+n/2+n/2=19n/2個

ワイヤは((11n+2)/2)*3+(n-1)+(n/2)*3+n+n/2=41n/2+2本

電源供給の10本を含めて41n/2+12本必要だと思った。

最上位の桁の繰り上がりも求めようとすると,マルチプレクサはn/2+1 ビット分いるの で,それに気がついてそのように計算している人もいましたが,それも当然正解ですが, 教科書ではそのように書いてないので,n/2ビット分で答えても構いません.

マルチプレクサのNOTは一つにまとめることができるので,それに気がついて減らしている 解答もありました.

cinを0や1に固定した場合は,加算器のゲート数を減らせることに気がつ いている解答もありました.

次に,同期式RSFFを2つ直列に用いてマスタースレーブ式RSFFを(図7.18)のように組み合わせると, 論理ゲートはNANDを8つ,NOTを1つ,ジャンプワイヤは19本必要である.

よって,マスタースレーブ型RSFFを2つ直列に用いてDFFを(図7.19)のように組み合わせると, 論理ゲートはさらにNOTを1つ,ジャンプワイヤを1つ多く使用することがわかる. つまり,論理ゲートはNANDを8つ,NOTを2つ,ジャンプワイヤは20本必要である.

上で考えたDFFをn個用いて,nビットのレジスタを(図7.21)のように組み合わせると, 論理ゲートはNANDを8n個,NOTを2n個必要なのは明らかである. また,ジャンプワイヤは,すべてのDFFに共通してしようする入力cのために1本増えるだけである.

よって,nビットのレジスタで必要となるのは, 論理ゲートが(NAND,NOT)で(8n,2n)本, ジャンプワイヤが20n+1本である.

ここで,今回の演習ではNOTを使えないことに気づいたので,他の論理ゲートでNOTを表す.

そのためには,入力信号を2つにわけてNANDに入力すればいい.

0→(0,0)→NAND→1か,1→(1,1)→NAND→0.

よって,論理ゲートはNOTからNANDに,ジャンプワイヤはNOT1個当たり1本増えることになる.

よって,nビットのレジスタで必要となるのは, 論理ゲートが(NAND)で(10n)本, ジャンプワイヤが21n+1本である.